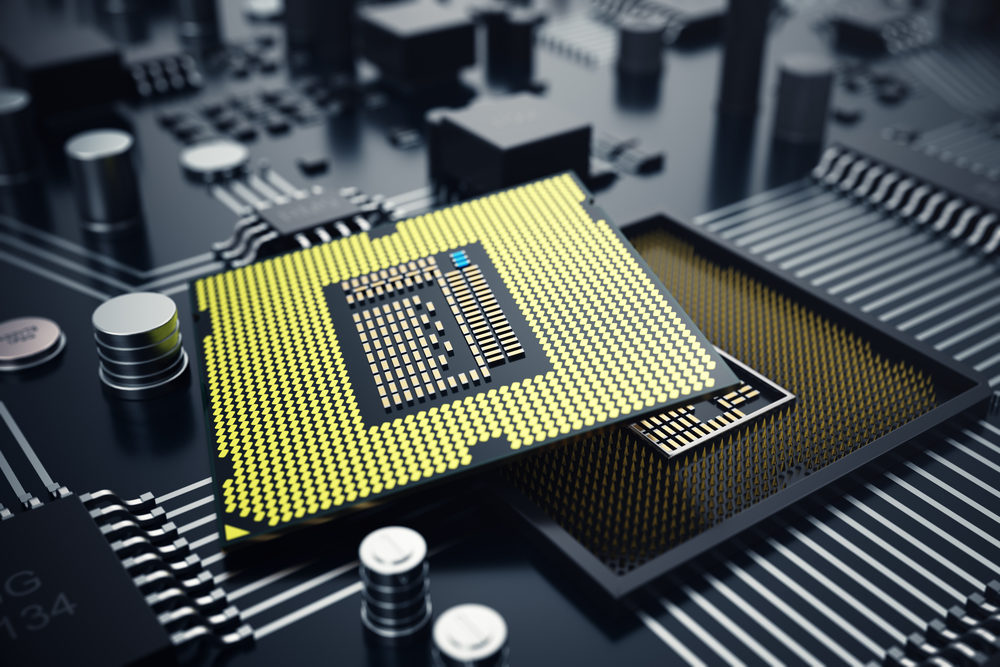

Online Physical Design Training course mainly focused on giving complete hands on experience to physical design and physical verification training flow with latest tools and full lab practice. By end of the course your will learn to work in Linux environment, understand complete physical design flow from partitioning, floor planning, power planning, timing analysis, clock tree synthesis, routing of a functional unit blocks to physical verification and sign-off checks.

It is extensive training for students in the field of electrical and electronics. Takshila VLSI ranks among the top 10 physical design training institutes in the Bangalore.