As modern chips squeeze billions of transistors into shrinking geometries, power has emerged as one of the most critical challenges in semiconductor design. Every new generation of devices demands higher performance with less energy, putting significant pressure on VLSI engineers to develop more innovative, more efficient solutions. Whether it’s smartphones, AI accelerators or automotive controllers, or edge computing devices, power efficiency affects battery life, thermal stability, reliability, and overall system performance. For students and engineers considering careers in chip design, learning low-power design concepts has become a necessity. Understanding how to analyse, reduce, and optimize power usage is a skill that could affect your entire journey in the VLSI industry.

1. The Growing Need for Power-Efficient Chip Design

The growing complexity of SoCs, higher operating frequencies, and increasing performance requirements have made Power optimization in VLSI a priority from the earliest design stages. The balance of performance, leakage, area, and power is now on engineers’ minds to stay within strict system specifications. As power budgets get smaller and the functionality of these chips grows, it’s even little gains in logic architecture or physical implementation that make a big difference in improving efficiency.

2. Reducing Power at the Switching Level

Managing switching activity remains one of the biggest opportunities for saving energy in digital circuits. This makes Dynamic power reduction methods essential in modern design flows. Engineers use strategies such as clock gating, glitch reduction, operand isolation, bus encoding, and logic simplification to minimize unnecessary transitions. Since dynamic power depends heavily on frequency, voltage, and switching events, optimizing these factors early ensures smoother timing, lower heat generation, and improved system reliability throughout the design.

3. Advanced Low-Power Techniques for Future Chip Designs

As technology nodes shrink, leakage power becomes as significant as dynamic power. That’s why next-generation chips are based on Advanced low-power design VLSI techniques such as gate-level optimization, transistor sizing, voltage islands, adaptive body biasing and multi-threshold logic. These techniques help the engineers to maintain efficiency while achieving performance goals. Understanding how these advanced methods work, especially in combination, helps new designers create well-balanced architectures for complex AI, wearable, and automotive chips.

4. Gating Power to Reduce Leakage and Improve Efficiency

One of the best and most effective leakage control strategies is Power gating in VLSI design. By closing the doors on unused blocks by switching off sleep transistors, engineers consume much less standby power. This technique is common in portable electronics, where it is important to have long battery life. Power gating also needs caution in managing wake-up times, domain boundary, isolation logic and retention strategies for smooth transitions during on/off states.

5. Common Industry Methods to Boost Power Efficiency

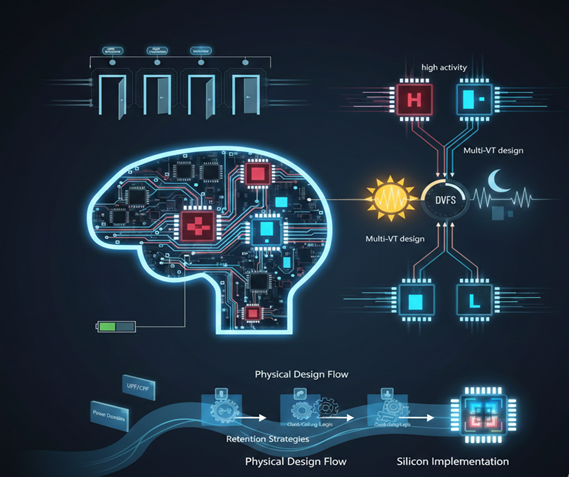

Once a foundation of basic strategies is understood, designers proceed into the actual engineering strategies. One major method is Multi-Vt design in VLSI, in which different threshold voltages are applied to different cells to balance leakage and performance. High-Vt cells minimize leakage and low-Vt cells provide speed-critical paths.

Another game-changing approach is DVFS (Dynamic Voltage and Frequency Scaling) in semiconductor design, which scales supply voltage and frequency to workload conditions. This helps save a lot of power during low activity without sacrificing performance when power is high.

At the physical design stage, the flow should be well-structured to retain power intent during implementation. Engineers define UPF/CPF constraints, power domains, retention strategies, and clock-gating logic to maintain consistency between logical design and silicon implementation.

6. Accurate Power Analysis for Smarter Design Decisions

Strong analytical skills are essential in low-power design. This is where the analysis of power methods used in VLSI comes in. Engineers use RTL power estimation, gate-level power simulation, and vector-based activity analysis to accurately measure energy consumption. With appropriate insights, they can change architectures, optimize logic structures, and optimize timing paths to achieve tremendous power savings.

Conclusion

Power optimization is no longer just a design goal, it is a necessity for every advanced VLSI chip. Engineers who understand how to balance performance, leakage, and efficiency create stronger, smarter, and more reliable designs. If you’re aiming to master these real-world techniques and grow into a skilled low-power engineer, takshila-vlsi continues to support learners with practical, industry-aligned VLSI training paths.